- 您现在的位置:买卖IC网 > Sheet目录317 > C8051F380-TB (Silicon Laboratories Inc)DEV KIT FOR C8051F38X

�� �

�

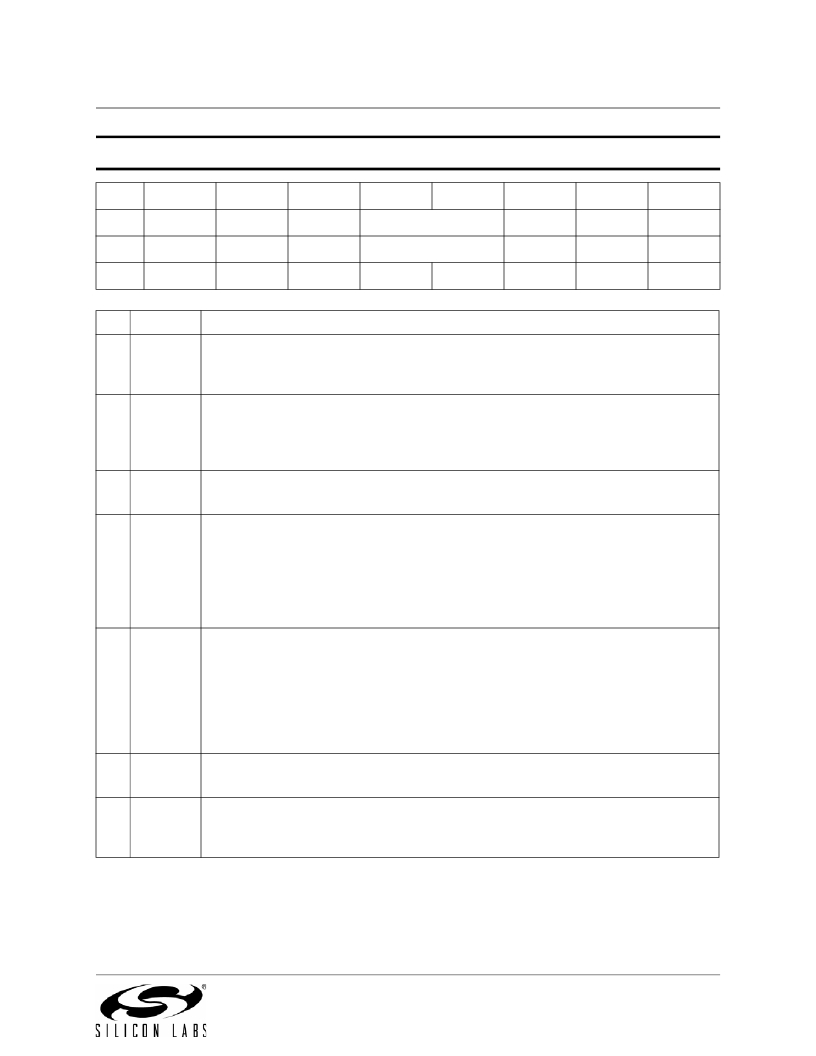

C8051F380/1/2/3/4/5/6/7/C�

�SFR� Definition� 11.6.� PSW:� Program� Status� Word�

�Bit�

�Name�

�Type�

�Reset�

�7�

�CY�

�R/W�

�0�

�6�

�AC�

�R/W�

�0�

�5�

�F0�

�R/W�

�0�

�4�

�0�

�RS[1:0]�

�R/W�

�3�

�0�

�2�

�OV�

�R/W�

�0�

�1�

�F1�

�R/W�

�0�

�0�

�PARITY�

�R�

�0�

�SFR� Address� =� 0xD0;� SFR� Page� =� All� Pages;� Bit-Addressable�

�Bit� Name� Function�

�7�

�6�

�5�

�4:3�

�2�

�1�

�0�

�CY�

�AC�

�F0�

�RS[1:0]�

�OV�

�F1�

�PARITY�

�Carry� Flag.�

�This� bit� is� set� when� the� last� arithmetic� operation� resulted� in� a� carry� (addition)� or� a� bor-�

�row� (subtraction).� It� is� cleared� to� logic� 0� by� all� other� arithmetic� operations.�

�Auxiliary� Carry� Flag.�

�This� bit� is� set� when� the� last� arithmetic� operation� resulted� in� a� carry� into� (addition)� or� a�

�borrow� from� (subtraction)� the� high� order� nibble.� It� is� cleared� to� logic� 0� by� all� other� arith-�

�metic� operations.�

�User� Flag� 0.�

�This� is� a� bit-addressable,� general� purpose� flag� for� use� under� software� control.�

�Register� Bank� Select.�

�These� bits� select� which� register� bank� is� used� during� register� accesses.�

�00:� Bank� 0,� Addresses� 0x00-0x07�

�01:� Bank� 1,� Addresses� 0x08-0x0F�

�10:� Bank� 2,� Addresses� 0x10-0x17�

�11:� Bank� 3,� Addresses� 0x18-0x1F�

�Overflow� Flag.�

�This� bit� is� set� to� 1� under� the� following� circumstances:�

�??� An�

�ADD,� ADDC,� or� SUBB� instruction� causes� a� sign-change� overflow.�

�??� A�

�MUL� instruction� results� in� an� overflow� (result� is� greater� than� 255).�

�??� A� DIV� instruction� causes� a� divide-by-zero� condition.�

�The� OV� bit� is� cleared� to� 0� by� the� ADD,� ADDC,� SUBB,� MUL,� and� DIV� instructions� in� all�

�other� cases.�

�User� Flag� 1.�

�This� is� a� bit-addressable,� general� purpose� flag� for� use� under� software� control.�

�Parity� Flag.�

�This� bit� is� set� to� logic� 1� if� the� sum� of� the� eight� bits� in� the� accumulator� is� odd� and� cleared�

�if� the� sum� is� even.�

�Rev.� 1.4�

�87�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

C8051F912DK

KIT DEV FOR C8051F91X/C8051F90X

C8051F930-TB

BOARD TARGET/PROTO W/C8051F930

C8051T610DB24

DAUGHTER BOARD T610 24QFN SOCKET

C8051T630DB20

BOARD SOCKET DAUGHTER 20-QFN

CAN-100

BOARD EVAL RS232 100QFP

CANADAPT28

KIT ADAPTER CANDEMOBOARD 28PLCC

CAT24AA01WI-GT3

IC EEPROM SERIAL 1KB I2C 8SOIC

CAT24AA02WI-G

IC EEPROM SERIAL 2KB I2C 8SOIC

相关代理商/技术参数

C8051F381

制造商:SILABS 制造商全称:SILABS 功能描述:USB DRIVER CUSTOMIZATION

C8051F381-GM

功能描述:8位微控制器 -MCU USB-64K-Flash

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F381-GMR

功能描述:8位微控制器 -MCU USB-Flash-64k-ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F381-GQ

功能描述:8位微控制器 -MCU USB-64K-Flash

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F381-GQR

功能描述:8位微控制器 -MCU USB-Flash-64k-ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F382

制造商:SILABS 制造商全称:SILABS 功能描述:USB DRIVER CUSTOMIZATION

C8051F382-GQ

功能描述:8位微控制器 -MCU USB-Flash-32k-ADC

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F382-GQR

功能描述:8位微控制器 -MCU USB-Flash-32k-ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT